# A New Topology of H-bridge based Multilevel Inverter for PV System with Reduced Switches

S.R.Nandhini<sup>1</sup>, G.Akalya<sup>2</sup>, K.Aswini<sup>3</sup>, K.Nandhini<sup>4</sup>, M.Valan Rajkumar<sup>5</sup>, B.Rajeshkumar<sup>6</sup> Department of Electrical and Electronics Engineering, Gnanamani College of Technology, Namakkal-637018, India.

Abstract: Multilevel inverter concept is the very important alternative in the field of medium and high power industrial drive applications. This new type of converters is suitable for high voltage and high power applications due to their ability to synthesize with better harmonic spectrum. By increasing the number of output levels in multilevel inverter, Total Harmonic Distortion (THD) can be minimized. It works under with the help of single phase with different pulse width modulation (PWM) techniques, Several PWM techniques are available, among them the level shifting SPWM techniques are used and comparison is based on the basis of total obtained. R2014a harmonics distortions version of MATLAB/Simulink software is used for simulation.

Index-Terms: Multilevel inverter (MLIs), Asymmetrical cascaded Multilevel Inverter (ACMLI), PWM techniques and Total Harmonic Distortion (THD).

## 1. INTRODUCTION

Multi-level power conversion is used to provide more than two voltage level to achieve smoother and less distorted dc to ac power conversion and it can generate a multiple-step voltage waveform with less distortion, less switching frequency and higher efficiency. Multilevel inverters have become more popular over the years in high power and high voltage applications. Whereas conventional two level inverter have some limitations in high power high voltage applications due to switching losses and power ratings [1-5].

Multilevel inverter offers several advantages over two-level inverter: it improves the output voltage waveform, reduced (dv/dt) voltage stress on the load and also reduces electromagnetic interference problems, but it has some disadvantages when the number of voltage levels increases such as; complex PWM controlling method, voltage balancing problems are introduced and higher number of semiconductor switches are required.

Each switch requires a separate gate driver circuit, therefore increasing the complexity and size of the overall circuit. For this problem, lower voltage rated switches can be used in multilevel inverter instead of higher number of semiconductor switches which can be used to minimized cost of the semiconductor switches as compared to two level inverters [6-8]. There are different conventional multi-level inverters topology mainly classified as Diode clamped multilevel inverter (DCMLI) [9-10], Flying capacitor inverter (FCMLI), cascaded H-bridge multilevel inverter (CHBMLI).

In 1981 a three level diode clamped multilevel inverter schemes proposed in [11]. The flying capacitor inverter structure is similar to that of diode clamped inverter but the main difference is that instead of clamping diodes, flying Capacitors are used. The control method of cascaded H Bridge multilevel is more convenient than other multilevel inverter because it doesn't have any clamping diode and flying capacitor. Cascaded multilevel inverter reaches higher reliability [12-15].

The cascaded inverter is used for large automotive electric drives. However, the requirement of more number of switches and separate dc source for each cell becomes a problem especially at higher level. Cascaded h-bridge multilevel inverter consists of separate dc links for each h-bridge cell so it is easily controllable. Cascaded h-bridge multilevel inverter has some drawback that by increasing the number of voltage levels numbers of switching devices given by 2(N+1) also increase [16].

This paper proposes a 21-level multi-level inverter with ACMIL topology which requires less number of switches and gate driver circuits as compared to conventional multilevel inverters.

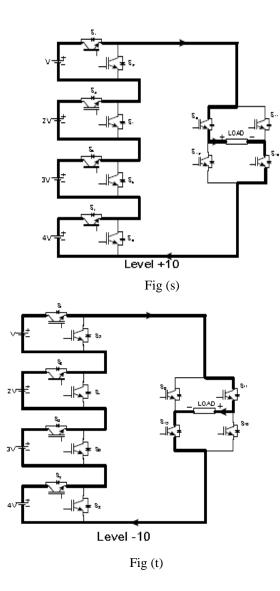

The proposed multilevel inverter topology [17-25] here is implemented in single-phase with different PWM techniques. The pulse-width modulation (PWM) control is the most efficient technique of controlling output voltage within the inverters. The carrier based PWM schemes used for multilevel inverters is the most efficient method, realized by the intersection of a modulating signal with triangular carrier waveform. The paper tries to prove that ACMIL topology is better than conventional multilevel inverters topology in terms of their number of components and THD.

#### 2. PROPOSED TOPOLOGY

A single DC supply to output voltages two level 0 and V. It is used two switches S1 and S2. If switch S1 is ON, output voltage are V and switch S2 is ON output voltage are zero. Switches S1 and S2 are OFF simultaneously to avoid the occurrence of short circuit across the DC supply.

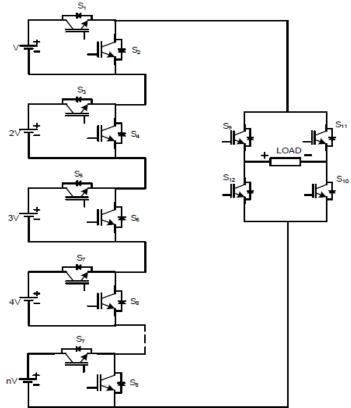

A three-phase asymmetrical n-level reduced devices cascading inverter shown in Fig.1 In this circuit, the DC-bus voltage is split into each cell. Which are connected in series and desired number of level can be achieved by series connection of switch.

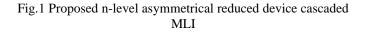

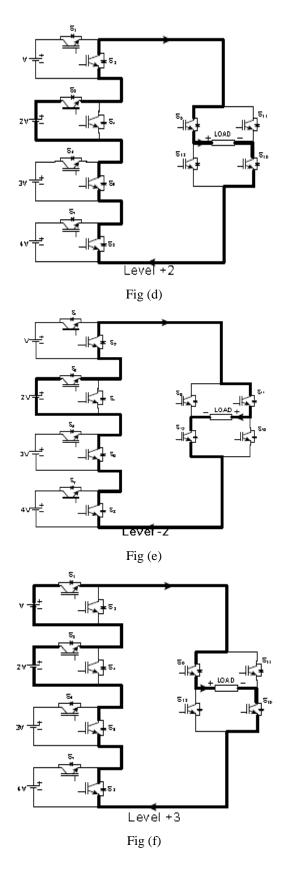

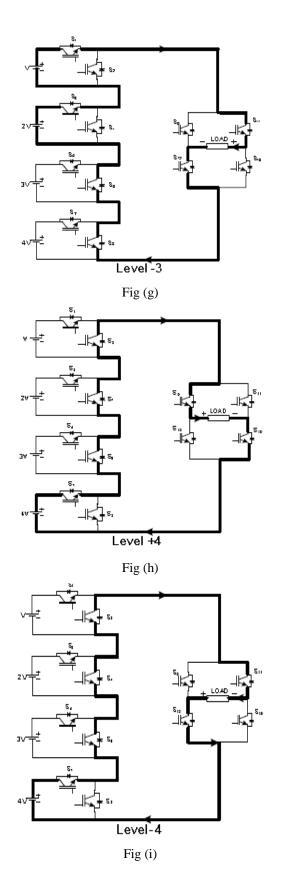

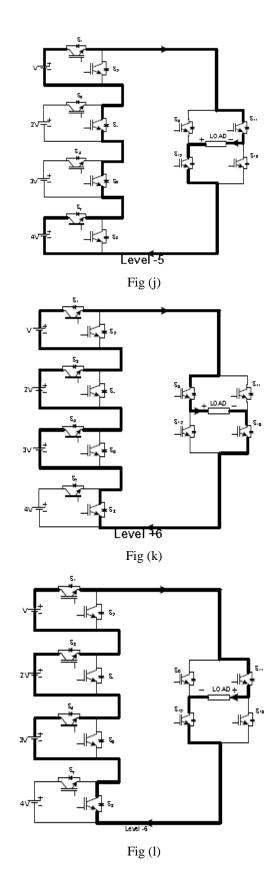

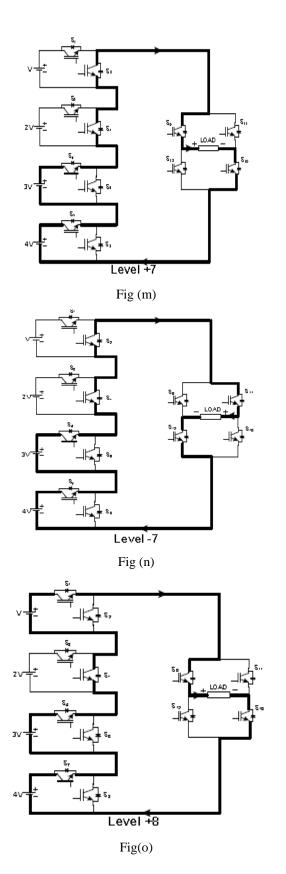

The proposed ACMLI topology for 21-level inverter requires twelve semiconductor switches and four isolated dc sources shown in Fig 2 [9] which separate output voltage in two parts. One part is called level generation part (left side) and is responsible for level generating in positive polarity & negative polarity.

The other part is called polarity generation part (right side) and is responsible for generating the polarity of the output voltage. This topology combines the two parts (left part and right part) to generate the multi-level output voltage waveform.

The main purpose of this proposed ACMLI topology is to control the EMI, minimize the total harmonic distortion with different PWM techniques and it also minimizes power semiconductor switches than conventional multilevel inverter.

For a conventional single-phase 21-level inverter, it uses 40 switches, whereas the proposed topology uses only 12 switches phase MLI with the same principle.

The proposed topology is a symmetrical topology because all the values of all voltage sources are equal. Therefore, it does not have voltage-unbalancing due to fixed dc voltage values.

### 3. OPERATION FOR THE PROPOSED TOPOLOGY

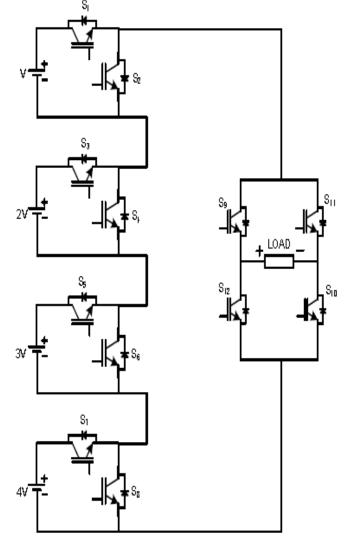

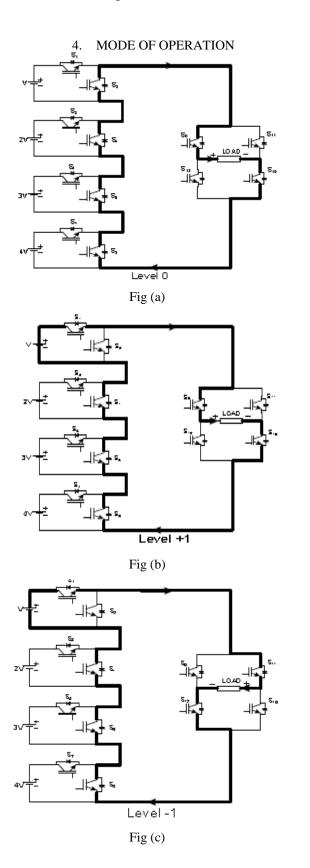

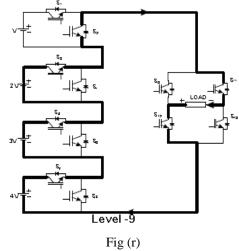

The operation of the proposed topology has been discussed in detail and has been verified with the help of with "10Vdc" (i.e., level +10). Operation of the proposed 21-level inverter.

Fig.2 Proposed single-phase asymmetrical cascade 21-level inverter for line to ground voltages

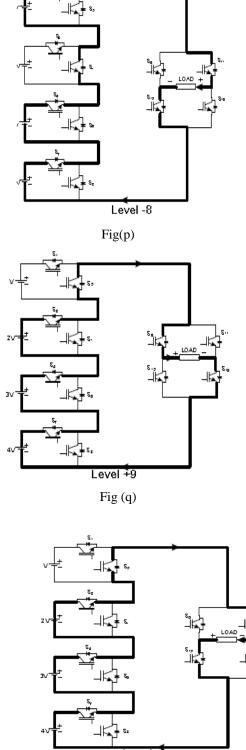

The output voltage will be "9Vdc" (i.e., level +9) when switches S2, S3, S5 and S7 are turned "on".

When S1, S4, S5 and S7 switches are turned "on" the output voltage will be "8Vdc" (i.e., level +8).

| Voltage<br>Level | Switching State       |                |                       |       |                       |       |                       |       |            |                |                        |                        | Output    |

|------------------|-----------------------|----------------|-----------------------|-------|-----------------------|-------|-----------------------|-------|------------|----------------|------------------------|------------------------|-----------|

|                  | <b>S</b> <sub>1</sub> | $\mathbf{S}_2$ | <b>S</b> <sub>3</sub> | $S_4$ | <b>S</b> <sub>5</sub> | $S_6$ | <b>S</b> <sub>7</sub> | $S_8$ | <b>S</b> 9 | ${\bf S}_{10}$ | <b>S</b> <sub>11</sub> | <b>S</b> <sub>12</sub> | - Voltage |

| +10              | 1                     | 0              | 1                     | 0     | 1                     | 0     | 1                     | 0     | 1          | 1              | 0                      | 0                      | 10V       |

| +9               | 0                     | 1              | 1                     | 0     | 1                     | 0     | 1                     | 0     | 1          | 1              | 0                      | 0                      | 9V        |

| +8               | 1                     | 0              | 0                     | 1     | 1                     | 0     | 1                     | 0     | 1          | 1              | 0                      | 0                      | 8V        |

| +7               | 0                     | 1              | 0                     | 1     | 1                     | 0     | 1                     | 0     | 1          | 1              | 0                      | 0                      | 7V        |

| +6               | 1                     | 0              | 1                     | 0     | 1                     | 0     | 0                     | 1     | 1          | 1              | 0                      | 0                      | 6V        |

| +5               | 1                     | 0              | 0                     | 1     | 0                     | 1     | 1                     | 0     | 1          | 1              | 0                      | 0                      | 5V        |

| +4               | 0                     | 1              | 0                     | 1     | 0                     | 1     | 1                     | 0     | 1          | 1              | 0                      | 0                      | 4V        |

| +3               | 1                     | 0              | 1                     | 0     | 0                     | 1     | 0                     | 1     | 1          | 1              | 0                      | 0                      | 3V        |

| +2               | 0                     | 1              | 1                     | 0     | 0                     | 1     | 0                     | 1     | 1          | 1              | 0                      | 0                      | 2V        |

| +1               | 1                     | 0              | 0                     | 1     | 0                     | 1     | 0                     | 1     | 1          | 1              | 0                      | 0                      | V         |

| 0                | 0                     | 1              | 0                     | 1     | 0                     | 1     | 0                     | 1     | 1          | 1              | 0                      | 0                      | 0         |

| -1               | 1                     | 0              | 0                     | 1     | 0                     | 1     | 0                     | 1     | 0          | 0              | 1                      | 1                      | -V        |

| -2               | 0                     | 1              | 1                     | 0     | 0                     | 1     | 0                     | 1     | 0          | 0              | 1                      | 1                      | -2V       |

| -3               | 1                     | 0              | 1                     | 0     | 0                     | 1     | 0                     | 1     | 0          | 0              | 1                      | 1                      | -3V       |

| -4               | 0                     | 1              | 0                     | 1     | 0                     | 1     | 1                     | 0     | 0          | 0              | 1                      | 1                      | -4V       |

| -5               | 1                     | 0              | 0                     | 1     | 0                     | 1     | 1                     | 0     | 0          | 0              | 1                      | 1                      | -5V       |

| -6               | 1                     | 0              | 1                     | 0     | 1                     | 0     | 0                     | 1     | 0          | 0              | 1                      | 1                      | -6V       |

| -7               | 0                     | 1              | 0                     | 1     | 1                     | 0     | 1                     | 0     | 0          | 0              | 1                      | 1                      | -7V       |

| -8               | 1                     | 0              | 0                     | 1     | 1                     | 0     | 1                     | 0     | 0          | 0              | 1                      | 1                      | -8V       |

| -9               | 0                     | 1              | 1                     | 0     | 1                     | 0     | 1                     | 0     | 0          | 0              | 1                      | 1                      | -9V       |

| -10              | 1                     | 0              | 1                     | 0     | 1                     | 0     | 1                     | 0     | 0          | 0              | 1                      | 1                      | -10V      |

# Table1 Switching States of Proposed Scheme

©EverScience Publications

©EverScience Publications

## 5. MODULATION STRATEGIES

When switches  $S_1$ ,  $S_3$ ,  $S_5$  and  $S_7$  are turned "on" the output voltage will be the output voltage will be "5Vdc" (i.e., level +5). When switches  $S_1$ ,  $S_4$ ,  $S_6$  and  $S_7$  are turned "on". When  $S_2$ ,  $S_4$ ,  $S_6$  and  $S_7$  switches are turned "on" the output voltage will be "4Vdc" (i.e., level +4).

When switches S2, S4, S5 and S7 are turned on the output voltage will be "7Vdc" (i.e., level +7). When switches S1, S3, S5 and S8 are turned "on" the output voltage will be "6Vdc" (i.e., level +6).asymmetrical cascaded topology can be easily explained with the help of fig. 2 and table I. continuous current operation the current of both thyristors overlaps.

When switches  $S_1$ ,  $S_3$ ,  $S_6$  and  $S_8$  are turned on the output voltage will be "3Vdc" (i.e., level +3). The output voltage will be "2Vdc" (i.e., level +2) when switches  $S_2$ ,  $S_3$ ,  $S_6$  and  $S_8$  are turned "on". When  $S_1$ ,  $S_4$ ,  $S_6$  and  $S_8$  switches are turned "on" the output voltage will be "V dc" (i.e., level +1). When switches  $S_2$ ,  $S_4$ ,  $S_6$  and  $S_8$  are turned "on" the output voltage is zero (i.e., level 0). Switches  $S_9$ ,  $S_{10}$ ,  $S_{11}$  and  $S_{12}$  are used for a complementary pair. When  $S_{10}$  and  $S_{11}$  are turned "on" together, positive half cycle (level: +1, +2, +3, and +4) can be generated and when  $S_9$  and  $S_{12}$ are turned "on" together, negative half cycle (level: -1, -2, -3, and -4) can be generated across load.

But the increase of level adds to the cost of converter and more number of secondary windings. So, a suitable compromise has to be made between the THD of the line current and cost of additional hardware. When the circuit works in inverter mode, the dc source transfers power to the main (ac source). The THD and Power flow analysis is done for various configuration of switching angles. The effect of variation of dc voltage on the THD and the power transfer is also analyzed. Though a battery has been considered as a dc source for simulation as well as experimental analysis, the result obtained can be utilized when using solar PV panel. The major advantage of the proposed configuration is that in continuous current mode of operation, the waveform resembles a stepped sinusoidal wave and with suitable selection of switching angles the harmonic contents can be reduced drastically. In general, the load current can be either continuous or discontinuous.

There are different pulse width modulation strategies as given below [12-13].Phase disposition pulse width modulation (PD PWM):- In phase disposition pulse width modulation strategy, where all carrier waveforms are in same phase. Phase opposition disposition pulse width modulation (POD PWM):- In phase opposition disposition pulse width modulation strategy, where all carrier waveforms above zero reference are in phase and below zero reference are 1800 out of phase. Alternate phase opposition disposition pulse width modulation (APOD PWM):-In alternate phase opposition disposition PWM scheme where every carrier waveform is in out of phase with its neighbor carrier by 180'.

Phase-shifted pulse width modulation (PS PWM):- A carrier phase shifted PWM for multi-level inverter is used to generate the stepped multi-level output voltage waveform with lower percentage THD. In proposed, before implementing the Multicarrier PWM Techniques, the gating signals of multi-level inverter switches are generated by comparing sinusoidal reference wave with triangular carrier waves at specific intervals of time producing the characteristic multistep output waveform. MLI with N levels requires (N-1) triangular carriers. In phase shifted PWM, all the triangular carriers have same frequency and same peak to peak amplitude.

## 6. SIMULATION RESULTS

The Fig.1 & 2 shows the proposed topology model of singlephase n-level & single-phase 21-level ACMLI. Table II shows THD comparison between different PWM techniques.

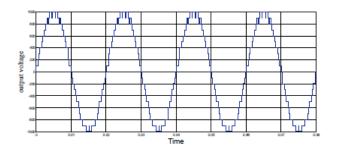

The simulation parameters are as following R = 10 ohms, L = 10 mH, and dc source voltage is 400V; Carrier signal frequency is 1 kHz. In this paper, four PWM techniques are used PD, POD, APOD, PS, VF and CO with different modulation index (Ma). For Ma = 1.0, and Mf = 20, corresponding (%) THD are PS = 5.54, PD = 5.78, POD = 6.01, APOD = 5.10, shown in Fig. 6.

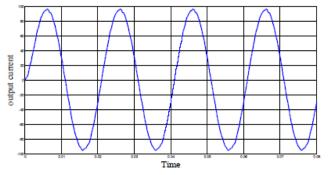

Fig.4 Single-Phase current by PSPWM for 24-level inverter with R-L load

Fig.5Single-Phase Voltage by PSPWM for 24-level inverter with R-L load  $% \left( {{{\rm{A}}_{\rm{B}}}} \right)$

Fig. 6 FFT analysis by PSPWM for R-L load (Ma=1.0, Mf=20).

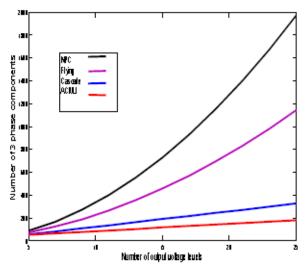

Fig.7 Required number of single phase components for different multi-level inverter topologies.

Fig. 7 shows the required number of single phase components for different multilevel inverter topologies. So it is clearly shows that the proposed ACMLI topology is requires less number of components than other conventional topologies so as the voltage level increases the number of components will decreases particularly for higher voltage levels [14-15].

### 7. CONCLUSION

In this paper, a new topology of 21-levels is proposed with reduced number of switches and DC sources. It is proved that, the proposed work of Single phase 21-level MLI output voltage total harmonics distortion is reduced and improve the efficiency of system compare with different conventional topologies of single phase and three-phase 21-level MLI. Harmonic analysis carried out using MATLAB R2014a version software. This proposed MLI topology requires less number of components as compared to conventional MLI inverters. The scheme has

successfully been implemented and tested by using R2014a version of MATLAB/Simulink software.

#### REFERENCES

- A. Chel, G.N. Tiwari, A. Chandra, Simplified method of sizing and life cycle cost assessment of buildings integrated photovoltaic system, Energy and Buildings 41 (2009) 1172-1180.

- [2] F. Blaabjerg, Z. Chen, S. Kjaer, Power electronics as efficient interface in dispersed power generation systems, IEEE Transactions on Power Electronics 19 (2004) 1184-1194.

- [3] M.ValanRajkumar, P.S.Manoharan, Modeling and Simulation of Threephase DCMLI using SVPWM for Photovoltaic System, Springer Lecture Notes in Electrical Engineering, under the volume titled "Power Electronics & Renewable Energy Systems", Volume 326, Chapter No 5, January 2015, Pages 39-45.

- [4] M.ValanRajkumar, P.S.Manoharan, Harmonic Reduction of Fuzzy PI Controller based Three-Phase Seven-level DCMLI with SVPWM for Grid Connected Photovoltaic System, Journal International Review on Modeling and Simulations, Volume 6, No 3, June 2013, Pages 684-692.

- [5] S. Subiyanto, A. Mohamed, M.A. Hannan, Intelligent maximum power point tracking for PV system using Hopfield neutral network optimized fuzzy logic controller, Energy and Buildings 51 (2012) 29-38.

- [6] M.ValanRajkumar, P.S.Manoharan, FPGA Based Multilevel Cascaded Inverters with SVPWM Algorithm for Photovoltaic system, Elsevier Journal Solar Energy, Volume 87, Issue 1, January 2013, Pages 229-245.

- [7] LianLian Jiang, Douglas L. Maskell, Jagdish C. Patra, A novel ant colony optimization-based maximum power point tracking for photovoltaic systems under partially shaded conditions, Energy and Buildings 58 (2013) 227-236.

- [8] Jose Rodriguez, Jih-Sheng Lai, Fang Zheng Peng, Multilevel inverters: a survey of topologies, controls, and applications, IEEE Transactions on Industrial Electronics 49 (2002) 724-738.

- [9] Colak, Ilhami, Kabalci, Ersan, Bayindir, Ramazan, Review of multilevel voltage source inverter topologies and control schemes, Energy Conversion and Management 52 (2011) 1114-1128.

- [10] P.Thirumurugan, P.S.Manoharan, M.ValanRajkumar, VLSI Based Space Vector Pulse Width Modulation Switching Control in the proceedings of IEEE International Conference on Advanced Communication Control and Computing Technologies ICACCCT 2012 on August 2012, ISBN No. 978-1-4673-2045-0 (Print) (Page):366-370.

- [11] M.ValanRajkumar, P.S.Manoharan, Space Vector Pulse Width Modulation of Three-Phase DCMLI with Neuro-Fuzzy MPPT for Photovoltaic System, World Journal of Modelling and Simulation, Volume 10, No 3, August 2014, Pages 193-205.

- [12] Ghazanfari, A., Mokhtari, H. and Firouzi, M. (2012) Simple Voltage Balancing Approach for CHB Multilevel Inverter Considering Low Harmonic Content Based on a Hybrid Optimal Modulation Strategy. IEEE Transactions on Power Delivery, 27, 2150-2158.

- [13] M.Valan Rajkumar, Prakasam, P. and Manoharan, P.S. (2016) Investigational Validation of PV Based DCDMLI Using Simplified SVM Algorithm Utilizing FPGA Tied with Independent Sources. Circuits and Systems, Volume 7, No 11, 3831-3848. http://dx.doi.org/10.4236/cs.2016.711320

- [14] Kavousi, A., Vahidi, B., Salehi, R., Bakhshizadeh, M.K., Farokhnia, N. and Fathi, S.H. (2012) Application of the Bee Algorithm for Selective Harmonic Elimination Strategy in Multilevel Inverters. IEEE Transactions on Power Electronics, 27, 1689-1696. http://dx.doi.org/10.1109/TPEL.2011.2166124

- [15] M.ValanRajkumar, P.S.Manoharan, "Modeling, Simulation and Harmonic Reduction of Three-Phase Multilevel Cascaded Inverters with SVPWM for Photovoltaic System", Journal International Review on Modeling and Simulations, Volume 6, No. 2, April 2013, Pages 342-350. ISSN: 1974-9821 (Print), 1974-982X (Online)

- [16] M.ValanRajkumar, P.S.Manoharan, "Modeling and Simulation of Fivelevel Five-phase Voltage Source Inverter for Photovoltaic Systems", Journal PrzegladElektrotechniczny, Volume 10, No. 10, October 2013, Pages 237-241. ISSN: 0033-2097 (Print)

- [17] A.Ravi, P.S.Manoharan, M.ValanRajkumar, "Harmonic Reduction of Three-Phase Multilevel Inverter for Grid connected Photovoltaic System using Closed Loop Switching Control", Journal-IREMOS, Volume 5, No 5, October 2012, Pages 1934-1942. ISSN: 1974-9821 (Print), 1974-982X (Online)

- [18] P.Thirumurugan, P.S.Manoharan, M.ValanRajkumar, "VLSI Based Inverter Switching Control" in the proceedings of International Conference on Mathematical Modeling and Applied Soft Computing MMASC'12 – Coimbatore Institute of Technology on July 2012, Vol-2 (Page):965-973.

- [19] IEEE Std 929-2000 (2002) Recommended Practices for Utility Interface of Photovoltaic System. The Institute of Electrical and Electronics Engineers.

- [20] C.Hemalatha, M.Valan Rajkumar, G.Vidhya Krishnan, "Simulation and Analysis for MPPT Control with Modified firefly algorithm for photovoltaic system", International Journal of Innovative Studies in Sciences and Engineering Technology, Volume 2, No 11, Nov.2016, Pages 48-52.

- [21] G.Vidhya Krishnan, M.Valan Rajkumar, C.Hemalatha, "Modeling and Simulation of 13-level Cascaded Hybrid Multilevel Inverter with less number of Switches", International Journal of Innovative Studies in Sciences and Engineering Technology, Volume 2, No 11, Nov.2016, Pages 43-47.

- [22] B. Sanjay Gandhi, S. Sam Chelladurai, and Dr. D. Senthil Kumaran, "Process Optimization for Biodiesel Synthesis from Jatropha Curcas Oil", Taylor & Francis-Distributed Generation and Alternative Energy Journal, Vol.23, No.4, Page 6- 16, 2011.

- [23] B. Sanjay Gandhi and D. Senthil Kumaran, "The Production and Optimization of Biodiesel from Crude Jatropha Curcas Oil by a Two Step Process— An Indian Case Study Using Response Surface Methodology", Taylor & Francis-International Journal of Green Energy, Vol.113, No.10, Page 1084-1096, 2014.

- [24] S. Chandrasekar and Gian Carlo Montanari, "Analysis of Partial Discharge Characteristics of Natural Esters as Dielectric Fluid for Electric Power Apparatus Applications," IEEE Transactions on Dielectrics and Electrical Insulation, Vol. 21, No. 3, pp.1251-1259, June 2014.

- [25] V.Jayaprakash Narayanan, B.Karthik and S.Chandrasekar," Flashover Prediction of Polymeric Insulators Using PD Signal Time-Frequency Analysis and BPA Neural Network Technique," Journal of Electrical Engineering and Technology. Vol. 9, Issue 4, pp. 1375-1384, 2014